原子层沉积技术突破:1000:1高深宽比涂层重塑半导体制造

半导体制造的"不可能任务"被攻克了

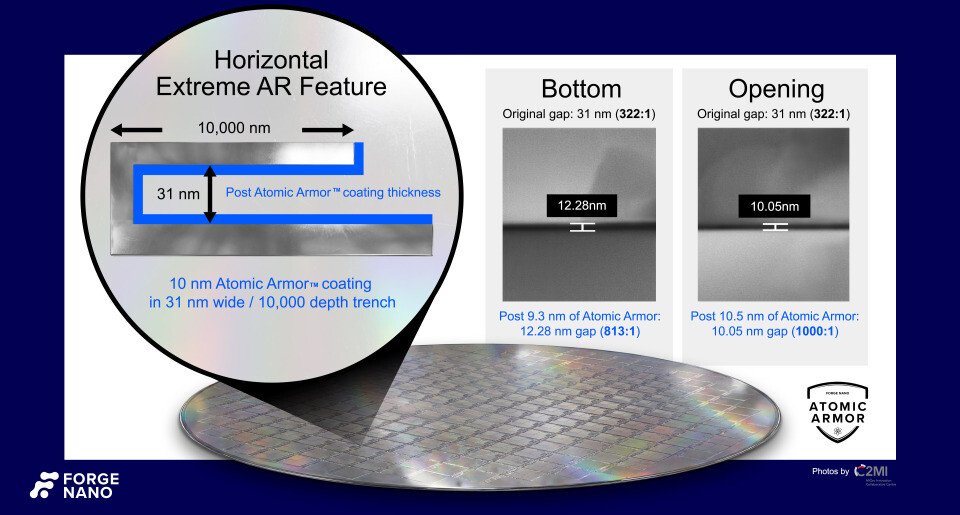

想象一下,要在比头发丝还细的沟槽里均匀涂上一层只有几个原子厚的薄膜,而且这个沟槽的深度是宽度的1000倍——这听起来像是科幻小说里的情节,但Forge Nano公司刚刚把这个"不可能任务"变成了现实。

什么是原子层沉积?为什么它如此重要?

原子层沉积(ALD)技术就像是给芯片"穿衣服"的纳米级裁缝。它通过交替通入不同的前驱体气体,在基底表面逐层沉积原子,形成均匀、致密的薄膜。这种技术对于制造3D NAND闪存、DRAM和先进逻辑芯片至关重要。

但传统ALD技术有个致命弱点:当芯片结构越来越复杂,沟槽越来越深时,薄膜的均匀性就会大打折扣。这就像试图用喷漆枪给一个深井的内壁均匀上色——底部的涂层总是比顶部薄。

Forge Nano的"黑科技"到底有多牛?

Forge Nano这次展示的技术突破可以用三个关键词概括:高速、无缺陷、1000:1深宽比。

- 速度革命:传统ALD工艺慢得像蜗牛,而Forge Nano的技术能在生产规模下保持高速沉积

- 质量保证:缺陷率低到可以忽略不计,这对于良率至上的芯片制造来说简直是福音

- 深度突破:1000:1的深宽比意味着他们能在极其复杂的3D结构中保持涂层均匀性

更厉害的是,这项技术的覆盖能力比传统的"视线技术"高出两个数量级。简单来说,就是能"看到"并涂覆传统方法根本触及不到的区域。

这会对芯片行业产生什么影响?

这项突破的意义不亚于当年FinFET晶体管的问世。它直接解决了限制3D半导体微缩的主要瓶颈,让一些原本被认为不经济甚至不可能实现的芯片架构成为可能。

想象一下未来的芯片:

- 存储芯片:3D NAND可以堆叠更多层,容量翻倍增长

- 逻辑芯片:晶体管密度进一步提升,性能更强、功耗更低

- 成本下降:制造良率提高,先进芯片的价格有望变得更亲民

Forge Nano与加拿大领先的半导体工艺开发中心C2MI合作,在实际生产级晶圆上进行了演示。合作伙伴的内部计量和可靠性测试独立验证了涂层的均匀性、缺陷率和电性能——这可不是实验室里的"玩具",而是随时可以投入生产的成熟技术。

中国半导体行业的机会与挑战

对于正在努力追赶先进制程的中国半导体产业来说,这项技术突破既是机遇也是挑战。一方面,它可能为国内企业提供"弯道超车"的技术路径;另一方面,如果国外企业率先大规模应用,技术差距可能会进一步拉大。

不过,好消息是原子层沉积设备不像EUV光刻机那样受到严格出口管制。国内的相关企业和研究机构完全可以考虑与Forge Nano合作,或者加大自主研发力度。

写在最后

半导体行业有句老话:"晶体管不撒谎"。一项技术是否真的突破,最终要看它能否在量产中稳定发挥。Forge Nano的这项成果已经通过了生产级验证,接下来就看它何时能大规模商用,以及会给整个行业带来怎样的变革了。

或许用不了多久,我们就能用上更便宜、性能更强的芯片——而这背后,正是像Forge Nano这样的公司在纳米世界里完成的"不可能任务"。毕竟,在半导体行业,今天的科幻往往就是明天的标准配置。