英特尔EMIB-T今年量产,AI芯片封装战局生变

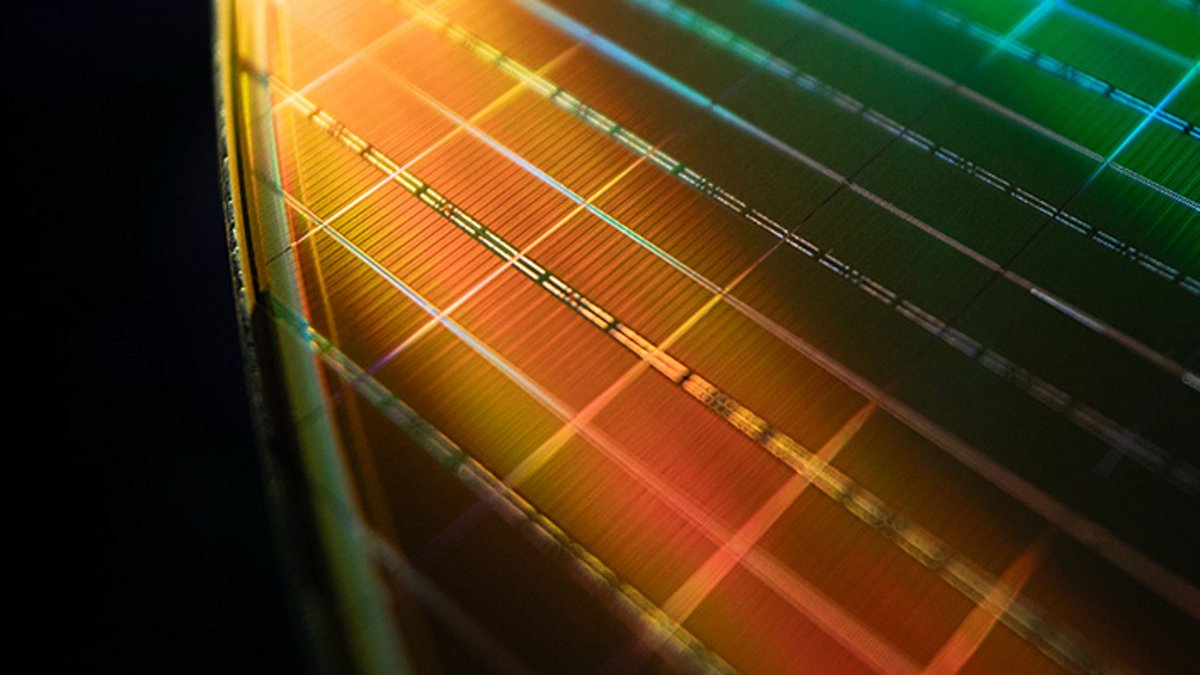

封装技术成AI芯片新战场

当大家都在关注制程纳米数字的军备竞赛时,一场发生在芯片封装层的暗战正在悄然升级。英特尔最近透露,其下一代EMIB-T封装技术将在今年实现量产,这可不是普通的工艺迭代——它直接瞄准了当下最火热的AI加速器市场,而台积电的CoWoS产能目前正面临“结构性供不应求”的尴尬局面。

从“绕路供电”到“垂直直达”

要理解EMIB-T的意义,得先看看它的前身。标准EMIB技术自2017年量产以来,一直采用在有机基板中嵌入硅桥的方式连接芯片,这种设计虽然成本低廉,但有个致命弱点:电力传输需要“绕远路”。

想象一下,电力就像快递员,原本可以直接上楼送货(垂直传输),但现在必须绕大楼一圈从侧门进入(水平传输)。对于普通CPU来说,这种绕路尚可接受,但对于功耗惊人的HBM4级AI加速器来说,这种“电阻式路径”就成了性能瓶颈。

EMIB-T的突破就在于增加了TSV(硅通孔)技术。简单来说,它给电力系统开了“直达电梯”——现在电力可以直接穿过硅桥垂直输送,同时集成了金属-绝缘体-金属电容器来抑制噪声,还增加了铜接地网格来隔离信号。这种设计让EMIB-T能够支持HBM3到未来HBM5的内存堆栈,封装尺寸最大可达120mm x 180mm,容纳超过38个桥接芯片和12个光罩尺寸的芯片。

数字背后的野心

英特尔封装技术开发副总裁Rahul Manepalli博士去年披露的数据显示,EMIB-T的凸点间距为45微米,未来将缩小至25微米,能效约为0.25皮焦/比特,数据传输速率达32Gb/s或更高。更令人印象深刻的是,英特尔在圣诞节前展示的概念设计中,一个2.5D/3D封装集成了16个计算单元、24个HBM5堆栈,硅面积达到10,296平方毫米。

这个尺寸意味着什么?它相当于12倍光罩尺寸,直接超越了台积电计划中9.5倍光罩的CoWoS-L上限。按照路线图,台积电今年目标是5.5倍光罩,2027年达到9.5倍;而英特尔则计划2026年实现8倍,2028年突破12倍。这不仅仅是数字游戏——更大的封装尺寸意味着能集成更多芯片,对于需要海量计算核心的AI模型来说,这是实打实的竞争优势。

成本与产能的双重优势

伯恩斯坦分析师估计,EMIB封装每个芯片的成本在几百美元低位,而台积电CoWoS在Rubin级加速器上约为900-1000美元。英特尔还声称其桥接芯片的晶圆利用率约为90%,而大型中介层的利用率只有60%左右。在芯片制造成本日益敏感的今天,这30个百分点的差距可能就是客户选择的关键因素。

当然,台积电也没有坐以待毙。其CoWoS产能已从2024年底的每月约3.5万片晶圆扩大到2025年底的约8万片,并计划通过嘉义AP7和台南AP8的新设施,在今年底达到约13万片。Counterpoint Research预计,这种积极的产能扩张将缓解目前的供应紧张,但英特尔此时推出EMIB-T,显然是想在台积电产能完全释放前抢占市场先机。

英特尔代工的“救命稻草”?

对于英特尔代工业务来说,EMIB-T可能不只是技术突破那么简单。英特尔首席财务官Dave Zinsner上个月透露,仅先进封装一项,英特尔代工就“接近达成一些每年价值数十亿美元的交易”。如果这些交易真的落地,那将是真正的逆转——去年英特尔代工外部收入仅为3.07亿美元,运营亏损却高达103亿美元。

考虑到英特尔18A制程最早也要明年才能达到行业标准良率,封装技术就成了英特尔最快的“上坡道”。EMIB-T如果成功,不仅能带来AI加速器收入,还可能成为英特尔代工业务翻身的转折点。最近英特尔宣布加入马斯克的Terafab项目,虽然外界对其能否兑现所有承诺持谨慎乐观态度,但这至少显示了英特尔在代工领域的野心。

在这场AI芯片的封装战争中,EMIB-T的登场不仅是一场技术升级,更可能重塑整个行业格局。当台积电还在为产能发愁时,英特尔已经准备好了替代方案——这场好戏,才刚刚开始。